Work History

Patent Litgation Code Reviews |

2010 to Present |

- I perform patent litigation software and hardware code reviews. This involves reviewing technical software or hardware implementations to determine if the design infringes patents or trade secrets.

- My work for Patent Litigation matters was paid (through 2010 to present) by: Precedia Associates LCC. in Palo Alto, CA, Finnegan Henderson Farabow Garrett & Dunner LLP in Palo Alto, CA, Google in Mountain View, CA, UnitedLex in Overland Park KS, O’Melveny & Myers LLP, San Francisco Ca, and Teklicon Inc. in San Jose, CA.

- My CV is available that lists the legal matters I have worked on.

ESS Technology

Dec 2000 to Aug 2019

Fremont, Ca

Distinguished Technologist

VP of Engineering

- My last title was Distinguished Technologiest & HW/SW Program Manager.

- As the VP of Engineering, I was in charge of IC design & software groups located in Beijing, Canada and California.

- The Fremont group is responsible for the Crescendo Soundbar products, the Ensemble codecs, the Compo audio products and other SOC designs. The SOC style products are mixed signal designs which include a SIMD engine, a 32 bit RISC and multiple DSPs.

- The Canadian group designed the industry’s highest performing audio DAC (the Sabre DAC) with a DNR of 135dB and a THD+N of 120dB. The Sabre ADC that has a DNR of 127dB and a THD+N of 120dB. The audio DACs are in production and are used in many high end audiophile consumer products. The audio product line consists of a family of parts ranging from the high performance high cost parts to the fully integrated ow cost and low BOM product.

- I am also in charge of software groups writing embedded software for various consumer products. For the SOC products this includes the video software required for the internal SIMD, RISC, and DSPs. There is embedded controller software for communication through the Ethernet, HDMI and USB interfaces. For the audio software there are various DSP algorithms for sound effects as required by the customers. The groups also work on PC based software for filter design and other software tools.

ESS Technology

(from Dec 2000 to Dec 2006)

VP of Communication IC Engineering

- I was in charge of 4 engineering groups that designed communication and/or video integrated circuits. This included a circuit group in Fremont, a logic group in Fremont, an analog group in Fremont and another analog group in Canada.

- The Fremont logic group designed video chips for DVD, other video consumer products, home networking, LAN, modem, DSPs, and RISCs.

- The Fremont analog group designs transceivers for the communication products and for the recordable DVD products.

- The Fremont circuit group supports the other groups for place and route, layout, pads, PLLs, etc.

- The Canadian analog group designs analog circuits for video consumer products. This includes specialized ADCs, DACs, RF, servo, and Class-D amplifiers.

- I personally worked on library characterization, on a DSP for the communication products and product debug.

Summit Semiconductor

Dec 1999 to Dec 2000

Los Gatos, Ca

VP of Engineering

- I incorporated myself as this company for contract work during this period specializing in custom circuit design, design intellectual property, and engineering services.

MKNet Corp

Sept 1999 to Dec 1999

San Jose, Ca

VP of Engineering

- I managed the engineering groups for a new infra-red start-up which required the development of a Very Fast Infra-Red (VFIR) 16Mb/s solution that includes a digital controller chip, a Bi-CMOS analog transceiver chip and software.

ESS Technology

1993 to 1999

Fremont, Ca

VP of Audio, VP of IC and R&D

- I managed the IC group for the development of the PC audio product line (mixed signal). This product line was very successful and ESS went public. The company grew from 40 to over 400 employees through my employment time period and the production volume grew to over 2.5 million mixed signal audio chips shipped per month.

- The audio design group I managed was less than 20 engineers that produced two high volume IC products each year and several minor designs. This group contained architects, logic designers, circuit designers, firmware engineers, patch developers, layout, IC routing, PCB design, and technicians.

- I also managed the software group (about 15 software engineers) that were responsible for the Windows drivers and application software.

- I personally designed the RISC processor as well as the standard cells, pads, some memories, and some other logic sections used within the designs. As a manager my personal design work was limited to feature requirements that engineers reporting to me could not design. The RISC processor was a true single cycle design that improved the software performance by about 6x, improved the operating power supply range and eliminated royalty payments.

- This group also designed general MIDI wavetable chips and 3D sound effect chips.

- We also successfully defended the company in a major patent lawsuit with a much larger competitor.

NARA

1986 to 1993

San Jose, Ca

VP of R&D

- This was a small engineering service company that made money by reverse engineering ICs and designing PC chip sets. I worked on the 82xx peripherals and other PC related designs including the DMA controller, counter/timer, interrupt controller, real time clock, VGA, XGA, UARTs, floppy disk controller, embedded controllers, and x86 processors. Using a semi-custom datapath design approach I was able to reduce the transistor counts (gate count) of these peripherals by a minimum of ˝ to a maximum of 1/7 of the previous designs.

- I wrote many software programs including a tool set for the automation of the reverse engineering of chips from scanned images to high level behavioral. I retain partial and full ownership of some software for dynamic timing logic simulation, design rule independent layout and other CAD/CAE software.

- I was used for several legal expert witness contracts including the AMD-INTEL co-processor lawsuits and for another processor company.

American Information Technology

1984 to 1986

San Jose, Ca

consultant

- I managed the circuit design group (as a consultant) for American Information Technology.

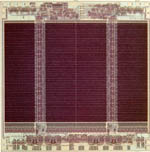

- At AIT I personally designed the execution unit datapath (custom transistor level design) of a 64 bit integrated processor and managed the engineers and layout designers for the rest of the processor and the required support chips (including graphics). I personally did much of the memory design, standard cell design and the initial place and route at AIT. I know it looks like it but I set up the router software and did the place and route on the chip shown above left before teaching a layout designer to take over the P&R task.

Zytrex

1981 to 1984

Sunnyvale, Ca

VP of Engineering, Director of Engineering

- After Texas I moved back to California to help start up a minor semiconductor company. The company grew from a 7-engineer living-room operation to a 200-man company including our own fab and assembly. Zytrex did go public and was listed on NASDAQ.

- After the first year, the company switched to using a unique high speed CMOS process (2u metal gate SATO devices with no field oxide) created by Frank Wanlass. I hired and managed a small group of engineers and layout designers that designed a total of more than 200 74HCTxx SSI and MSI part numbers using about 50 different mask sets. We also worked on high-speed multipliers and microprocessor 82xx peripheral products.

- For the first year of operation the company tried to supply Bi-CMOS ROMs. I designed other chips using “watch-chip” technology: 5 to 7 micron non-self-aligned channel lengths in metal gate. The inexpensive fab we had was very poor. We used contact printing mask aligners which limited our process technology.

- I was responsible for IC design and many other activities in the start-up including the purchasing, initial operation and programming of the IC test equipment, proto-type assembly equipment, and the CAD equipment.

MOSTEK

Carrolton, Tx

Design Engineer

- I was one of two design engineers working on a 32K pseudo static RAM. This design used a unique three transistor memory cell that was sustained using a charge pump.

- I received three US circuit design patents and presented a paper for the pseudo static at the 1981 ISSCC.

- I was the project manager of a 64K static RAM and worked on the 128K dynamic RAM project.

DRAM and SRAM Memory Cell Comparison

AMI

Santa Clara, Ca

Design Engineer

- My first product design out of school was a slow, 150ns, 1K by 4 VMOS static RAM (AMI 1560). I was then given a project manager lead for a high speed, 55ns, 1K by 4 VMOS static RAM (AMI 1599). The analog high-speed sense amp I created for the 1599 was used for years at various companies.

- Then I was the project manager for the first 16K static RAM in the industry (AMI 1600).

- Also, while I was at AMI, I worked on ROMs, dynamic RAMs and did some minor process development. The technology used for these designs were 4.5 micron VMOS transistors supplemented by 2.5 micron SATO (self-aligned by thick oxide) NMOS transistors with resistor loads. This product group was managed by T. J. Rodgers who later founded Cypress